Last updated: June 17th, 2024 at 08:45 UTC+02:00

SamMobile has affiliate and sponsored partnerships, we may earn a commission.

Reading time: 2 minutes

Samsung recently announced that it will be ready for the mass production of 2nm semiconductor chips next year and that this process will be further improved in 2027.

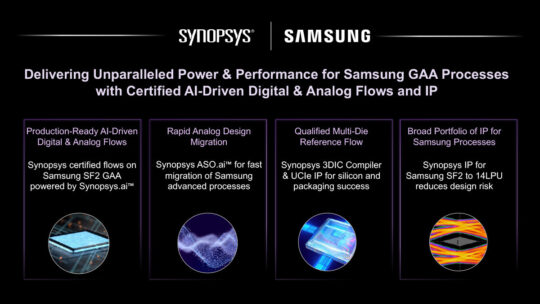

Chip design firms and clients interested in fabricating their chips using Samsung Foundry's 2nm process will be happy to know that Synopsys‘ AI-driven analog and digital design tools have received certification for that process node with multiple chip tape-outs.

Synopsys.ai is a full-stack Electronic Design Automation (EDA) suite that improves analog design migration, PPA, and productivity for Samsung Foundry's 2nm Gate All Around (GAA) process node. Synopsys' AI-driven design technology co-optimization (DTCO) solution has optimized Samsung's 2 nm process, improving area, performance, and power efficiency.

The Synopsys DSO.ai tool is used for design productivity and PPA optimization, while Synopsys ASO.ai is used for faster analog design migration. These processes have been applied for migrating designs from FinFET to GAA architecture, which means clients can migrate their chip designs used for the 8nm (or older) FinFET process to the new 2nm GAA process.

Chip firms can use Synopsys' tools to develop new chip design techniques, including backside power routing, local layout effect-aware methodology, and nanosheet cell design, for improved efficiency and higher performance with the SF2 process. Samsung Foundry's SF2Z process node can further improve performance, power, and area (by 20%).

The story continues after our video below, which compares the performance of the Exynos 2400 with that of the Snapdragon 8 Gen 3.

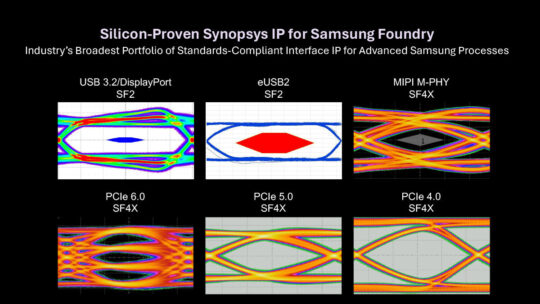

Synopsys UCIe IP has been used to tape out chips using the SF2 and SF4x processes for faster integration of chiplets in multi-die packages. Latency, power, and die-to-die connectivity were also improved in the SF5A process. Synopsys' 3DIC Compiler can be used for 2.5D and 3D heterogeneous integration and advanced packaging.

Moreover, Synopsys has revealed that the same DTCO solution will also be used to optimize Samsung Foundry's 1.4nm process node (SF1.4).

Asif is a computer engineer turned technology journalist. He has been using Samsung phones since 2004, and his current smartphone is the Galaxy S23 Ultra. He loves headphones, mechanical keyboards, and PC hardware. When not writing about technology, he likes watching crime and science fiction movies and TV shows.